Esta es la más importante y la más utilizada en la tecnología bipolar por su alta velocidad, alto Fan-Out y alta flexibilidad lógica. Independientemente de la función lógica implementada, la salida puede tener diferentes configuraciones de acuerdo a la aplicación que se quiera integrar:

CONFIGURACIÓN POR RESISTENCIA DE COLECTOR (NAND TTL)

La resistencia de polarización va integrada en el propio circuito integrado, pero presenta el problema de que cuando el transistor conduzca existe una disipación de potencia en la resitencia que provoca un calentamiento que hay que disipar, y esto impide un nivel alto de integración, por ello no se utiliza hoy en día.

CONFIGURACIÓN POR COLECTOR ABIERTO (NAND TTL)

Esta configuración es igual que la anterior con la diferencia que la resistencia de colector no está integrada en el circuito integrado, sino que es externa. Se utiliza para el gobierno directo de cargas que precisan unas tensiones y corriente superiores a los niveles de la familia. Por otro lado permiten la realización de puertas AND por conexión directa con solo unir en paralelo la salida de varios circuitos integrados.

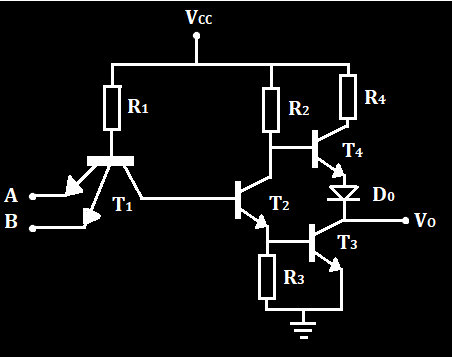

CONFIGURACIÓN TOTEM-POLE (NAND TTL)

Con esta configuración se consigue por un lado que cuando el transistor T4 conduce, el transistor T3 esté abierto, de esta manera, se consigue tener un estado lógico 1 en la salida, pero con la ventaja de que aunque pase corriente por el T4, como su caída de tensión es aproximadamente de 0,2V, su disipación de potencia es próxima a 0 mW y la potencia disipada por R4 es baja ya que ésta es del orden de 100 ohmios.

Por otro lado, cuando T3 conduce, T4 está abierto, provocando que la intensidad por T4 sea cercana a 0 mA y por tanto, la potencia disipada en él sea próxima a 0 mW. Además T3 conduce, su tensión Colector-Emisor es de 0,2V, siendo su potencia disipada del orden de 0 mW.

En ambos casos la potencia disipada es muy baja y permite un alto nivel de integración.

Es similar a la configuración Totem Pole, a la que se le ha añadido un nuevo emisor al transistor multiemisor T1, un transistor T5, una resistencia R5 y un diodo D1 y su funcionamiento es el siguiente:

Cuando se introduce un 1 lógico por la entrada de inhibición I del transistor T5, este conduce y el tercer emisor de T1 se fija al valor de saturación de la tensión Colector-Emisor del T5. Así, la unión Base-Emisor del transistor T1 pasa a conducir, y el diodo D1 también conduce. Esto provoca que T2, T3 y T4 estén en corte, con lo que la salida queda aislada, tanto a tierra como de la fuente Vcc, por una alta impedancia que es el tercer estado, independientemente de la configuración lógica que exista en ese momento en las entradas A y B.

Cuando se introduce un estado lógico 0 en la entrada de inhibición I, el transistor T5 no conduce y el diodo D1 tampoco, de manera que no se alter la tensión de colector de T2 funcionando para la puerta normalmente en su configuración TOTEM POLE.