Entre sus características cabe destacar:

La tensión de alimentación entre 4,75V y lso 5,25V.

Los niveles lógicos entre 0 y 0,8V para el nivel V(0) y entre 2,4 y Vcc para el nivel V(1).

Lavelocidad de transmisión rápida es su mejor característica, pero también esta, le hace aumentar su consumo. Para corregir el aumento de consumo, salieron versiones como la FAST, SL, L, etc.

Las señales TTL se degrada enseguida, haciendo necesarios circuitos adicionales para la transmisión.

INVERSOR BIPOLAR

Cuando la tensión de entrada es menor o igual que la tensión de corte, el transistor está cortado y desprecia la Intensidad de colector, por lo que la tensión de salida es igual a Vcc, es decir, tenemos un nivel V(1).

Cuando la tensión de entrada se vuelve ligeramente superior a la tensión de corte, la pequeña corriente de colector hace decrecer la tensión de salida teniendo en la misma un nivel V(0).

En resumen, el inversor se implementa mediante una etapa amplificadora en emisor común con una elección adecuada del valor de las resistencias, de manera que cuando la señal en la base del transistor conmuta entre los niveles lógico, la señal de colector también conmuta, así pues el transistor trabaja pasando de corte a saturación y viceversa. Este circuito presenta un Fan-Out bajo y un bajo margen de ruido.

En resumen, el inversor se implementa mediante una etapa amplificadora en emisor común con una elección adecuada del valor de las resistencias, de manera que cuando la señal en la base del transistor conmuta entre los niveles lógico, la señal de colector también conmuta, así pues el transistor trabaja pasando de corte a saturación y viceversa. Este circuito presenta un Fan-Out bajo y un bajo margen de ruido.

PUERTA NOR DE 3 ENTRADAS EN RTL

La lógica Resistencia-Transistor (RTL) es la clase más sencilla de circuitos digitales donde se utilizan transistores y resistencia para la conmutación.

En el caso de la puerta NOR, cada entrada utiliza un transistor bipolar, cuyos colectores están unidos y apoyados por la fuente de alimentación Vcc, a través de la resistencia de colector Rc. Este circuito utiliza una lógica positiva donde 1,8V es el valor mínimo para un 1 lógico y 0,2V es el valór máximo para un 0 lógico. Presenta un Fan-Out bajo y un bajo margen de ruido. Con este circuito se dan dos situaciones posibles, Todas las entradas a nivel lógico 0 con lo cual presenta un 1 lógico en la salida y La presencia de un uno lógico en cualquiera de sus entradas, presentaría un 0 lógico en la salida.

CASO A

Todas las entradas a nivel lógico 0

La intesidad de base en los tres transistores es igual al cero y por tanto , los tres transistores están en corte, por tanto, la tensión en la salida tiene a aproximarse a la tensión de alimentación Vcc y con ello se tiene un 1 lógico en la salida.

Para conocer el valor final de tensión de salida, es necesario saber el número de puertas conectadas a ella, cuanto más se conecten, menor será el valor de impedancia, y por tanto mayor la corriente de colector. Esta variación de corriente de colector, hará que también sea mayor la caida de tensión en la resistencia de colector. El límite se establece en evitar que se confuda el estado de alto.

CASO B

Alguna de las entradas presenta un 1 lógico

Cuando esto ocurre el transistor de esa entrada tiene en su base una tensión de1,8V que pone a ese transistor en saturación y por tanto, en dicho transistor la tensión de colector emisor es igual al valor de saturación, es decir, 0,2V, lo cual indica que en su salida hay la misma tensión, es decir un 0 lógico.

PUERTA NAND EN RTL

Tiene dos transistores de manera que le colector del primero está unido a la resistencia de colector y esta a su vez a la fuente de alimentación. Su emisor está conectado al colector del segundo transistor, que tiene el emisor conectado directo a masa. Las bases de ambos transistores son las entradas de la puerta.

La puerta trabaja en lógica positiva, y tiene dos posibles situaciones, cuando todas las entradas están a nivel lógico 1, teniendo en su salida un nivel 0 y cuando en alguna de sus entradas existe un nivel lógico 0, que provoca en su salida un nivel lógico 1.

CASO A

Cuando todas las entradas tienen un nivel lógico 1

En este caso ambos transistores conducen y por tanto, la tensión Colector-Emisor de ambos transistores es baja, lo cual nos da en la salida un 0 lógico

CASO B

Cuando una de las entradas tiene un nivel lógico 0

La intensidad de base correspondiente en prácticamente cero y dicho transistor estará en corte, quedando su intensidad de colector prácticamente en 0. Los transistores que estén por encima de él, no conducirán y los que estén por debajo de él, conducirán directamente a masa y la caida de tensión en la resistencia de colector será nula con lo cual eso provocará un 1 lógico en la salida.

PUERTA NOR EN DTL

La tecnología Diodo Transistor, sin olvidar las resistencias, son los diodos los que se encargan de realizar la parte lógica y el transistor actúa como amplificador e inversor. Al realizar la lógica los diodos y usar un transistor como sumador se obtiene un mejorado Fan-Out y un mejor margen de ruido, de hecho este tipo de circuitos es la base de la familia TTL.

Las dos situaciones que se pueden dar son todas las entradas a nivel lógico 0, con lo cual tendremos un nivel lógico 1 en la salida y alguna de las entradas tengan un nivel lógico 1 con lo que tendremos un nivel lógico 0 en la salida.

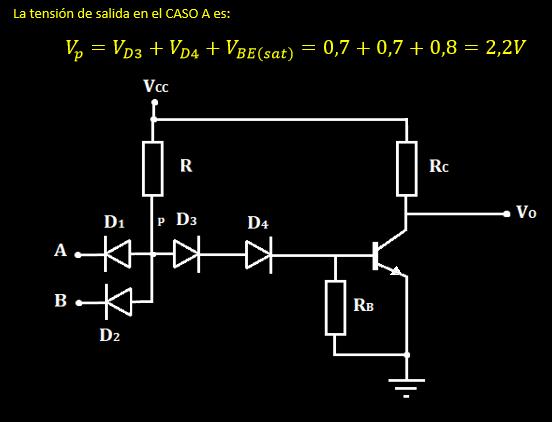

CASO A

Todas las entradas tiene nivel lógico 0

Para que el transistor conduzca, es necesario que en el punto p exita una tensión suficiente para hcer conducir a los diodos D3 y D4 y que todavía quede tensión suficiente para que el transistor pase a conducir, así el valor de tensión necesario en el punto p es de 2,2V. Como los diodo D1 y D2 no conducen, el punto p queda conectado a tierra a través de la resistencia pull down R= 6,1 K, resultando la tensión en dicho punto menos de 2,2 siendo insuficiente para polarizar el transistor en activa, de este modo la tensión de salida queda aislada de la tierra, siendo su valor aproximadamente al mismo que la Vcc, por tanto, la salida tendrá nivel lógico 1

CASO B

Alguna de las entradas tiene nivel lógico 1

En este caso, el diodo asociado a la entrada con el nivel lógico 1 conducirá y por tanto en el punto p tendremos una tensión de 4,3V donde, V gamma es el umbral del diodo que esta en conducción. Esta tensión hace conducir a los diodos D3 y D4 y al transistor, por lo que la tensión de salida es igual a la tensión Colector-Emisor del transistor que en saturación vale 0,2V y por tanto la salida tiene un nivel lógico 0

PUERTA NAND EN

DTL

CASO A

Alguna de las

entradas tiene nivel lógico 0

El diodo de

entrada que tenga el nivel lógico 0, pasará a conducir y por tanto, en el punto

p tendremos una tensión de:

Vp = V(0) + VDin = 0,2 + 0,7 = 0,9V

V(0) = Tensión del nivel lógico 0 que es 0,2V

VDin = Tensión de umbral de diodo de entrada en conducción que es 0,7V

Para que el

transistor conduzca la tensión en el punto P deber ser lo suficientemente alta

para hacer conducir a los diodos D3 y D4 y además quede tensión suficiente para

que el transistor pase a la zona de saturación, eso sería:

Vp = VD3 + VD4 + VBE sat = 0,7 + 0,7 + 0,8 = 2,2V

Como en el

punto p

=0,9V el transistor no conduce comportándose como un circuito abierto

desconectado la salida de tierra. La Intensidad de colecto es muy pequeña, casi

nula, lo que hace que la tensión se salida sea alta, casi la misma que la

fuente de alimentación lo cual tenemos un 1 lógico en la salida.

CASO B

Todas las entradas

tienen nivel lógico 1

Al tener en

todas las entradas un nivel lógico 1, los diodos de entrada no conducen, con lo

que habrá en el punto P una tensión igual a la tensión de alimentación Vcc

menos la caída de tensión en la resistencia R que es suficiente para hacer

conducir a éstos. En esta situación, la

tensión de salida será igual a la tensión colector-emisor de un transistor en

saturación que es 0,2V lo que equivale a un 0 Lógico